#### © 2022

Mohammadreza Soltaniyeh

ALL RIGHTS RESERVED

### HARDWARE-SOFTWARE TECHNIQUES FOR ACCELERATING SPARSE COMPUTATION

By

#### MOHAMMADREZA SOLTANIYEH

A dissertation submitted to the

School of Graduate Studies

Rutgers, The State University of New Jersey

In partial fulfillment of the requirements

For the degree of

Doctor of Philosophy

Graduate Program in Computer Science

Written under the direction of

Santosh Nagarakatte

And approved by

New Brunswick, New Jersey

October, 2022

ABSTRACT OF THE DISSERTATION

**Hardware-Software Techniques for Accelerating Sparse Computation**

by Mohammadreza Soltaniyeh

Dissertation Director: Prof. Santosh Nagarakatte

Linear algebra kernels are widely used in various fields such as machine learning, data

science, physical science, and graph analysis. Many of these applications work with sparse

data (i.e., only a small fraction of data is non-zero). Sparse data are often stored in a com-

pressed format (ie, sparse format) that stores only the non-zero elements with additional

metadata to identify where the non-zero elements are located. Using compressed formats

eliminates the need to store and process zeros, making the storage and computation of

sparse kernels more efficient.

General purpose architectures, such as CPUs and GPUs, are not able to deliver the

same performance for sparse linear algebra kernels as they do for dense versions. First, ac-

cessing non-zero elements in sparse format introduces many indirect and irregular memory

accesses incompatible with SIMD and caching mechanisms used by CPUs and GPUs. In

addition, Dennard scaling is obsolete and Moore's law is slowing down, ending the era in

which general-purpose architectures become faster and more energy efficient transparently.

This has led to a plethora of research into developing specialized hardware, such as FPGAs

and ASICs to improve the performance and energy efficiency of these sparse kernels. A

key strategy for the specialized hardware is to customize the sparse format (i.e., storage)

according to the operation memory access pattern, the pattern of non-zero elements in the

input (i.e., sparsity pattern), and the underlying hardware structures. This approach is effec-

ii

tive if the operations and input sparsity patterns do not change. However, applications often perform various operations on sparse data. Additionally, the sparse inputs may frequently change for each execution, and each input may have a different sparsity pattern. When this happens, the performance of specialized hardware degrades because a reformatting step is required to convert the data into a format that is compatible with the hardware. The data reformatting can be expensive when it cannot be overlapped with the computation on the hardware or amortized over multiple application executions with the same input data.

This dissertation presents a few hardware-software techniques that enhance the performance and energy efficiency of some of the most important sparse problems, including sparse matrix-vector multiplication (SpMV), sparse general matrix-matrix multiplication (SpGEMM), and sparse convolutional neural networks (CNNs). The key insight of our method is to use the software to reformat the sparse data into a hardware-friendly format, allowing the hardware to perform the computation with a high degree of parallelism. The software improves design flexibility by supporting multiple sparse formats, and the hardware improves performance and energy efficiency. We applied these hardware-software techniques to SpMV, SpGEMM, and sparse CNNs. These problems have different characteristics, such as different input densities and distinct input sparsity pattern features. The contribution of this dissertation can be summarized as follows. First, we present a synergistic CPU-FPGA system to accelerate SpMV and SpGEMM kernels. In our proposed design, the CPU reorganizes sparse data into a format suitable for the FPGA, and the FPGA computes with high parallelism using the preprocessed data. We develop an intermediate representation that allows the software to communicate regularized data and scheduling decisions to the FPGA. Besides, most of the CPU and FPGA execution are overlapped. Our approach can effectively handle sparse kernels with low input densities and sparsity patterns varying for each sparse input. Our end-to-end full system evaluation of the REAP prototype using Alveo-U200 FPGA has up to  $3.4\times$  and  $1.3\times$  speedup over the highly optimized Intel MKL library on a multicore CPU for SpMV and SpGEMM for widely-used sparse formats. Our results show that REAP achieves both high frequency and promising speedup compared to state-of-the-art FPGA accelerators for SpMV and SpGEMM while supporting various sparse formats and precision configurations. Second, we present a hardware accelerator for sparse CNN inference tasks. We formulate the convolution operation as general matrix-matrix multiplication (GEMM) using an image to column (IM2COL) transformation. With a dynamically reconfigurable GEMM and a novel IM2COL hardware unit, our design can support various layers in CNNs with high performance. Besides, our design exploits sparsity in both weights and feature maps. We use the software to perform group-wise pruning followed by a preprocessing step that puts the pruned weights into our hardware-friendly sparse format for efficient and high performance computation. We evaluated our accelerator using a cycle-level simulator and an HLS implementation realized on an Alveo FPGA board. Our ASIC design is on average 2.16×, 1.74×, and 1.63× faster than Gemmini, Eyeriss, and Sparse-PE, which are prior hardware accelerators for dense and sparse CNNs, respectively. Besides, our hardware accelerator is also 78×, and 12× more energy-efficient when compared to CPU and GPU implementations, respectively.

#### ACKNOWLEDGMENTS

Foremost, I would like to express my sincere gratitude to my advisor, Prof. Santosh Nagarakatte, for his support and guidance throughout my Ph.D. journey. Santosh spent countless hours teaching me how to think rigorously and critically, present ideas, and clearly express ideas in writing. His influence on how to think, present, and write will always remain with me.

I also extend my deepest gratitude to Prof. Richard P. Martin. His collaboration and guidance have been invaluable throughout my Ph.D.

I would also like to thank the other members of my Ph.D. committee, Prof. Yipeng Huang and Prof. Joe Devietti, for their thoughtful feedback about my research that has helped shape this dissertation.

Additionally, I would like to thank the Memory Solution team at Samsung Semiconductor, where I did two internships during my Ph.D. I particularly want to thank my mentors and manager, Veronica Lagrange Moutinho dos Reis, Matt Bryson, and Xuebin Yao, from whom I learned a lot.

I feel fortunate to have had the opportunity to learn from and interact with faculty members of the Computer Science Department at Rutgers University, particularly Abhishek Bhattacharjee, Srinivas Narayana, Sudarsun Kannan, Thu Nguyen, and all the other faculty that I have been able to learn from. I am especially thankful to Abhishek Bhattacharjee for providing valuable feedback about the initial directions of my research. I would also like to thank the administrative and technical staff at the Computer Science Department at Rutgers University for their support.

At Rutgers, I made some great friends who made this journey enjoyable. I want to thank my lab mates at RAPL group, David Menendez, Adarsh Yoga, Nader Boushehriinejad, Jay Lim, Sangeeta Chowdhary, Harishankar Vishwanathan, and Matan Shachnai, for their support. Beyond my lab, I was fortunate to meet some great friends, Guilherme, Zi Yan, Binh

Pham, Jan Vesely, Georgiana, and Jaewoo. They brought fun and a sense of motivation.

Last but not least, I would like to thank all my family for their unconditional love and support throughout the years. I would also like to thank Mahdi, Alireza, Kathryn, Shahab, Mahyar, Vahid, Shiva, and many other friends with whom I had the opportunity to have fun times.

To my family

#### TABLE OF CONTENTS

| Abstrac   | et       |                                                                                                                  | ii         |

|-----------|----------|------------------------------------------------------------------------------------------------------------------|------------|

| Acknow    | vledgme  | nts                                                                                                              | V          |

| List of T | Fables . | x                                                                                                                | ii         |

| List of I | Figures  | xi                                                                                                               | iii        |

| Chapter   | r 1: Int | roduction                                                                                                        | 1          |

| 1.1       | Dissert  | ration Statement                                                                                                 | 4          |

|           | 1.1.1    | Synergistic CPU-FPGA Acceleration for SpMV and SpGEMM                                                            | 5          |

|           | 1.1.2    | An Accelerator for Sparse Convolutional Neural Networks Leveraging Systolic General Matrix-Matrix Multiplication | 8          |

|           | 1.1.3    | A End-to-end FPGA Prototype of SPOTS for Sparse CNNs                                                             | 11         |

| 1.2       | Papers   | Related to this Dissertation                                                                                     | 12         |

| 1.3       | Dissert  | ration Organization                                                                                              | 13         |

| Chapte    | -        | rrse Linear Algebra Acceleration For Multiple Formats Using A U-FPGA System                                      | l <b>4</b> |

| 2.1       |          | ew of Our CPU-FPGA system for Accelerating Sparse Linear Algernels                                               | 15         |

|           | 2.1.1    | Contributions                                                                                                    | 17         |

| 2.2    | Background on Sparse Formats and Sparse Linear Algebra Kernels                               | 17                                                    |

|--------|----------------------------------------------------------------------------------------------|-------------------------------------------------------|

|        | 2.2.1 A Background on Sparse Formats                                                         | 18                                                    |

|        | 2.2.2 A Background on SpMV and SpGEMM kernels                                                | 20                                                    |

| 2.3    | Synergistic CPU-FPGA Acceleration                                                            | 23                                                    |

|        | 2.3.1 Instantiation of REAP to Accelerate SpMV                                               | 28                                                    |

|        | 2.3.2 Instantiation of REAP to Accelerate SPGEMM                                             | 32                                                    |

| 2.4    | Experimental Methodology of REAP                                                             | 39                                                    |

| 2.5    | Experimental Evaluation of REAP for SpMV and SpGEMM                                          | 42                                                    |

| 2.6    | Related Work on Accelerators for SpMV and SpGEMM Kernels                                     | 49                                                    |

| 2.7    | Summary                                                                                      | 52                                                    |

| Chapte | r 3: An ASIC Accelerator for Sparse Convolutional Neural Networks                            | 53                                                    |

| 3.1    | Overview of SPOTS                                                                            | 54                                                    |

|        | and a North Caroma                                                                           |                                                       |

|        | 3.1.1 Novelties of SPOTS                                                                     | 57                                                    |

| 3.2    | Background on CNNs, IM2CoL, and Sparsity-Awareness in CNNs                                   |                                                       |

| 3.2    |                                                                                              | 57                                                    |

| 3.2    | Background on CNNs, IM2COL, and Sparsity-Awareness in CNNs                                   | 57<br>57                                              |

| 3.2    | Background on CNNs, IM2CoL, and Sparsity-Awareness in CNNs 3.2.1 Convolution Neural Networks | 57<br>57<br>59                                        |

| 3.2    | Background on CNNs, IM2CoL, and Sparsity-Awareness in CNNs 3.2.1 Convolution Neural Networks | <ul><li>57</li><li>57</li><li>59</li><li>61</li></ul> |

|        | Background on CNNs, IM2COL, and Sparsity-Awareness in CNNs                                   | <ul><li>57</li><li>57</li><li>59</li><li>61</li></ul> |

|        | Background on CNNs, IM2COL, and Sparsity-Awareness in CNNs                                   | 577<br>579<br>611<br>622                              |

| 3.4    | SPOTS     | Our Hardware Accelerator for Sparse CNNs                                                     |

|--------|-----------|----------------------------------------------------------------------------------------------|

|        | 3.4.1     | The IM2Col Unit                                                                              |

|        | 3.4.2     | The GEMM Unit                                                                                |

|        | 3.4.3     | Handling Sparsity in CNNs                                                                    |

|        | 3.4.4     | Handling Various CNN Layers/Shapes                                                           |

|        | 3.4.5     | Strategies to Improve Load Balance in SPOTS                                                  |

| 3.5    | Related   | work                                                                                         |

| 3.6    | Summa     | ry                                                                                           |

| Chapte | r 4: An I | FPGA Accelerator for Sparse Convolutional Neural Networks 85                                 |

| 4.1    | Backgro   | ound on High Level Synthesis for FPGAs                                                       |

|        | 4.1.1     | Building FPGA Designs with High Level Synthesis                                              |

|        | 4.1.2     | HLS Optimizations                                                                            |

| 4.2    | The Arc   | chitecture of Our FPGA Accelerator for Sparse CNNs 91                                        |

|        | 4.2.1     | The IM2Col Unit                                                                              |

|        | 4.2.2     | The GEMM Unit                                                                                |

|        | 4.2.3     | Sparsity-aware Design                                                                        |

|        | 4.2.4     | Design Scalibility and Handling Various CNN Layers                                           |

| 4.3    | Related   | Work on FPGA Accelerators for CNNs                                                           |

| 4.4    | Summa     | ry                                                                                           |

| Chapte | _         | erimental Evaluation of our ASIC and FPGA Accelerators for rse Convolutional Neural Networks |

| 5 1    | Experin   | nental Methodology                                                                           |

| 5.2                                         | Experi  | mental Evaluation of SPOTS                                                           |  |

|---------------------------------------------|---------|--------------------------------------------------------------------------------------|--|

|                                             | 5.2.1   | Comparing the Speedup of SPOTS ASIC and FPGA Prototypes with CPUs and GPUs           |  |

|                                             | 5.2.2   | Comparing the Energy Efficiency of SPOTS ASIC and FPGA Prototypes with CPUs and GPUs |  |

|                                             | 5.2.3   | Comparing the Speedup of SPOTS ASIC Prototypes with Other ASIC Designs               |  |

|                                             | 5.2.4   | Performance Sensitivity to Different Layers' Shapes                                  |  |

|                                             | 5.2.5   | Performance and Energy Characterization of IM2CoL Unit 121                           |  |

|                                             | 5.2.6   | Load Imbalance in SPOTS                                                              |  |

| Chapter 6: Conclusion and Future Directions |         |                                                                                      |  |

| 6.1                                         | Disser  | tation Summary                                                                       |  |

| 6.2                                         | Directi | ions for Future Work                                                                 |  |

|                                             | 6.2.1   | Extending REAP to other Sparse Linear Algebra Kernels 125                            |  |

|                                             | 6.2.2   | Synthesizing Hardware Accelerators for Sparse Problems 126                           |  |

|                                             | 6.2.3   | Exploring New Programming Languages for Sparse Kernels on FP-GAs                     |  |

### LIST OF TABLES

| 2.1 | The CPU, and FPGA configurations                                                                                                                                                                |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2 | FPGA resource utilization for SpMV and SpGEMM designs                                                                                                                                           |

| 2.3 | List of matrices from SparseSuite [27] used in our evaluation 41                                                                                                                                |

| 2.4 | REAP speedup compared to a 16-core Intel MKL for SpMV and SpGEMM for three sparse formats and different input precisions                                                                        |

| 2.5 | Qualitative comparison of REAP with prior work that use FPGAs to accelerate sparse linear algebra kernels                                                                                       |

| 3.1 | Qualitative comparison of SPOTS with prior work                                                                                                                                                 |

| 5.1 | SPOTS ASIC design parameters and area                                                                                                                                                           |

| 5.2 | The CPU, GPU and FPGA configurations for SPOTS evaluation 108                                                                                                                                   |

| 5.3 | The FPGA configurations for SPOTS evaluation                                                                                                                                                    |

| 5.4 | FPGA resource utilization and operating frequency for two versions of SPOTS on Alveo U200                                                                                                       |

| 5.5 | Network characteristics, the top1, and top5 result accuracy, and the overall sparsity for the original (with no pruning), random pruning, and our structured pruning using the imagenet dataset |

| 5.6 | Comparing the performance and efficiency of SPOTS ASIC design with different ASIC designs for AlexNet and VGGNet                                                                                |

#### LIST OF FIGURES

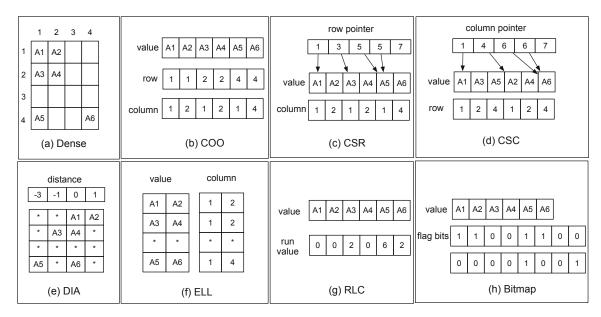

| 2.1  | An illustration of different sparse format representations, including COO, CSR, CSC, DIA, ELL, and RLC                              | 19 |

|------|-------------------------------------------------------------------------------------------------------------------------------------|----|

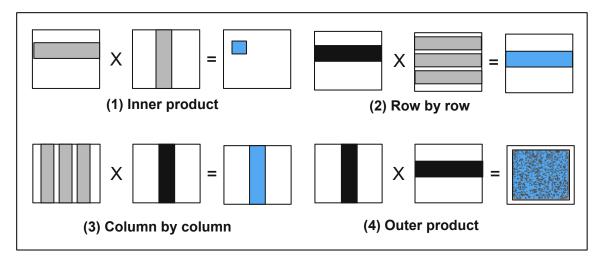

| 2.2  | An illustration of four different formulations to perform general matrix-matrix multiplication                                      | 21 |

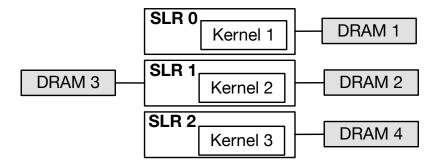

| 2.3  | The floorplan of XCU200 FPGA                                                                                                        | 25 |

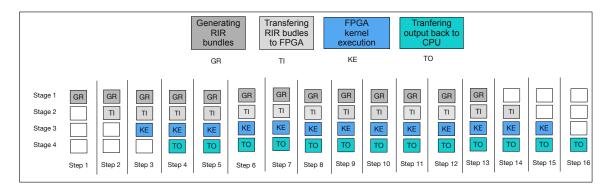

| 2.4  | An illustration of the overlapping of the tasks performed by the CPU and FPG tasks in REAP                                          | 27 |

| 2.5  | An illustration of RIR bundle generation for SpMV                                                                                   | 30 |

| 2.6  | An illustration of the FPGA design for SpMV                                                                                         | 31 |

| 2.7  | An illustration of RIR bundle generation for SpGEMM                                                                                 | 34 |

| 2.8  | Overall architecture of the FPGA dsign for SpGEMM                                                                                   | 34 |

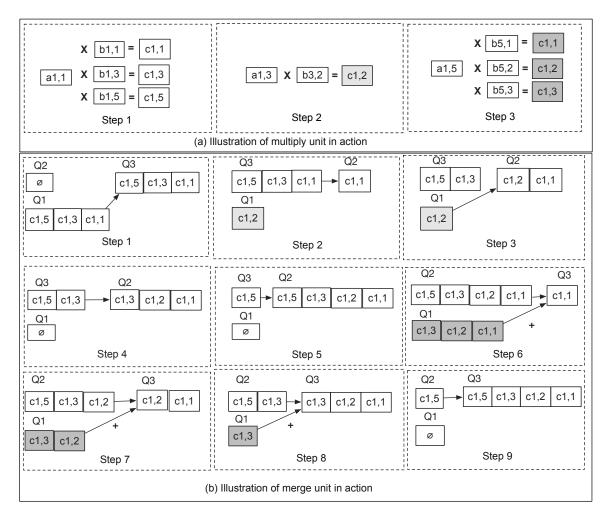

| 2.9  | An illustration of the multiply unit in action for SpGEMM design                                                                    | 35 |

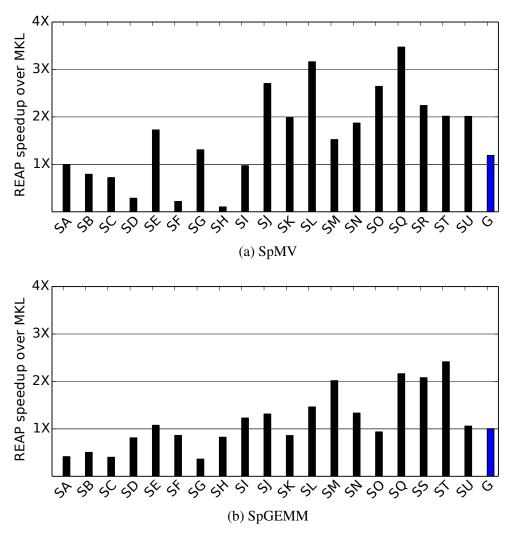

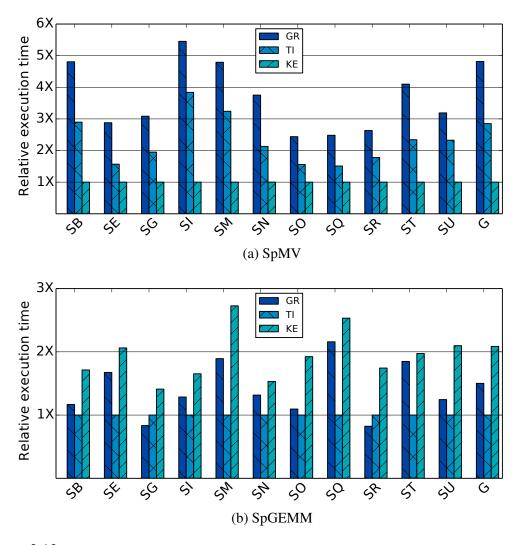

| 2.10 | Speedup of REAP compared to 16-core Intel MKL for the SpMV and SpGEMM kernels with single-precision inputs stored in the CSR format | 43 |

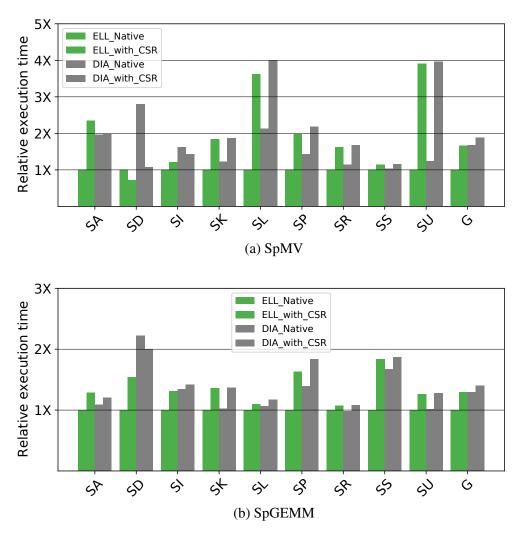

| 2.11 | Comparing the end-to-end execution time for two versions of ELL and DIA formats                                                     | 44 |

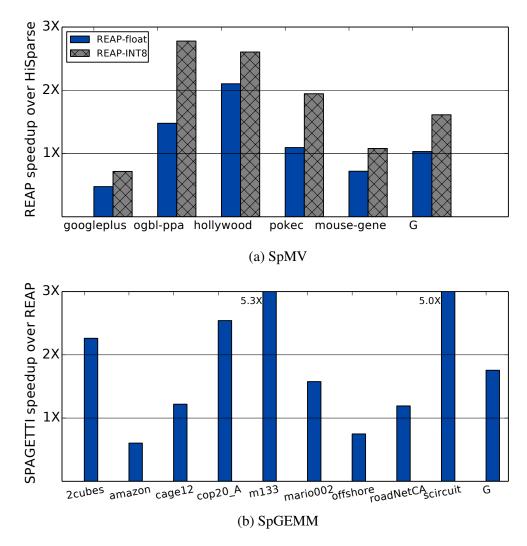

| 2.12 | Comparing REAP's speedup with the recent FPGA accelerators for SpMV and SpGEMM                                                      | 45 |

| 2.13 | REAP execution breakdown                                                                                                            | 47 |

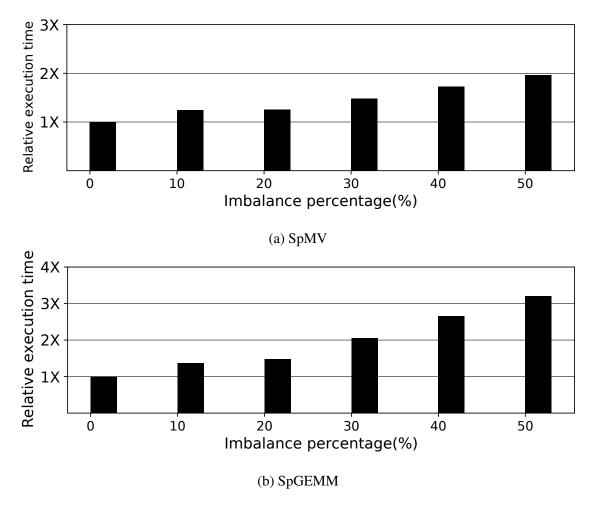

| 2.14 | Studying the impact of load imbalance on the FPGA execution time for SpGEMM and SpMV                                                | 49 |

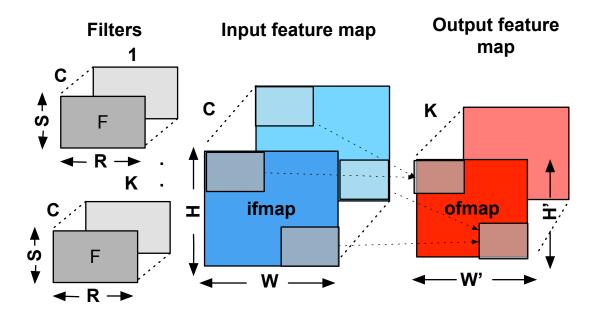

| 3.1  | An illustration of a convolution layer along with its inputs                                                                                                                              | 58  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

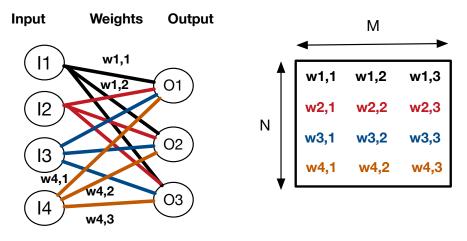

| 3.2  | An illustration of an FC layer and its matrix form                                                                                                                                        | 59  |

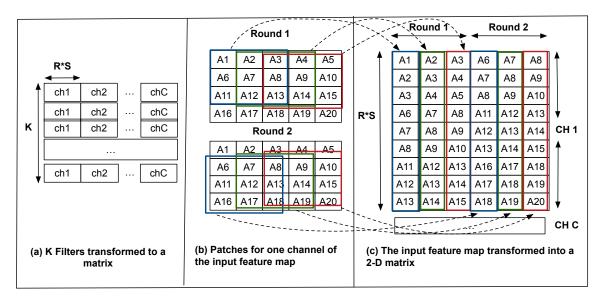

| 3.3  | An illustration of transforming a convolution layer to a GEMM computation.                                                                                                                | 60  |

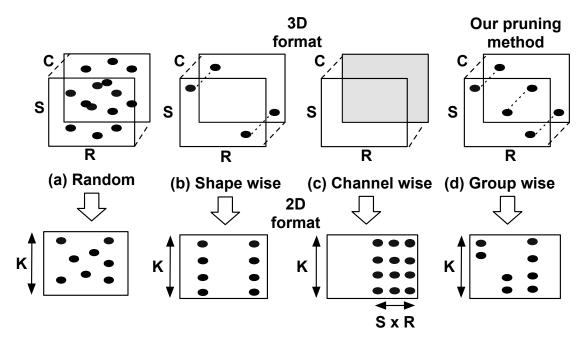

| 3.4  | A comparison of various pruning methods for CNNs                                                                                                                                          | 61  |

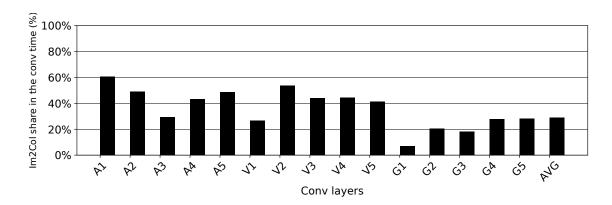

| 3.5  | An illustration showing the percentage of the total execution time spent in the IM2Col transformation for various convolution layers from AlexNet, VGGNet, and GoogleNet for a CPU system | 63  |

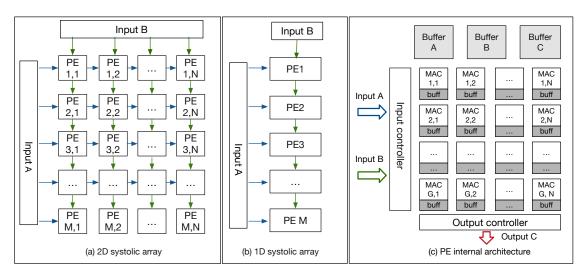

| 3.6  | The overall architecture of our accelerator with the IM2CoL unit and a systolic array-based GEMM unit                                                                                     | 67  |

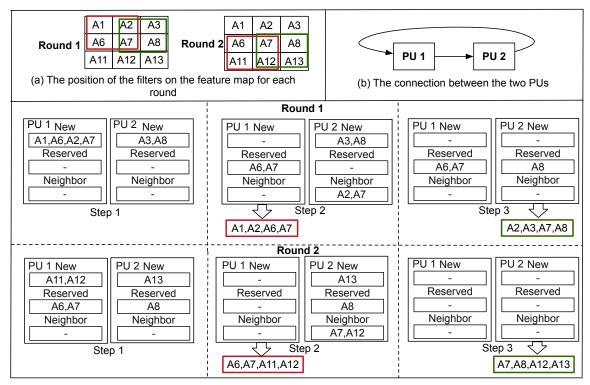

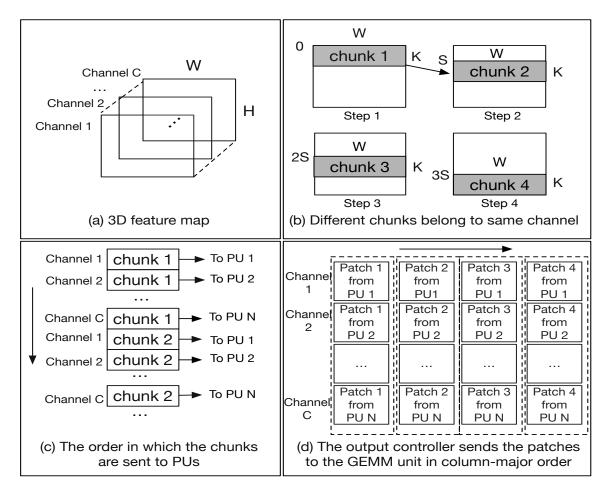

| 3.7  | An illustration of patch generation using the PUs in the IM2CoL unit                                                                                                                      | 68  |

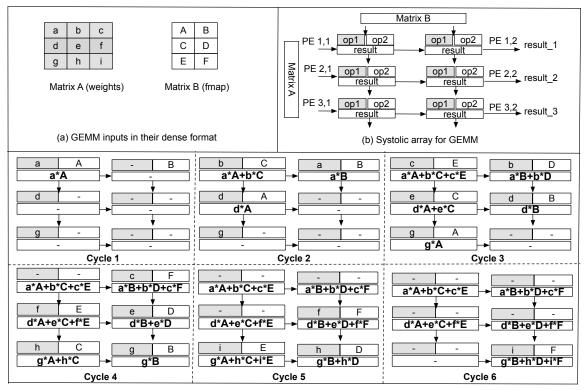

| 3.8  | An illustration of the GEMM unit in our accelerator                                                                                                                                       | 71  |

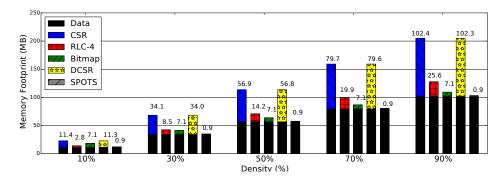

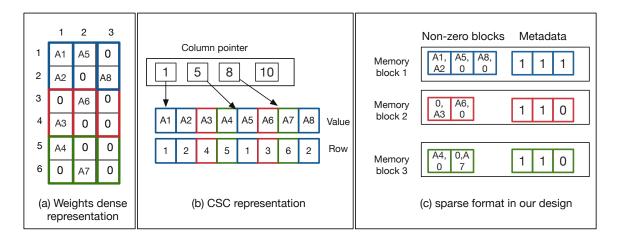

| 3.9  | A comparison of our proposed custom sparse format with other state-of-the-art sparse formats                                                                                              | 75  |

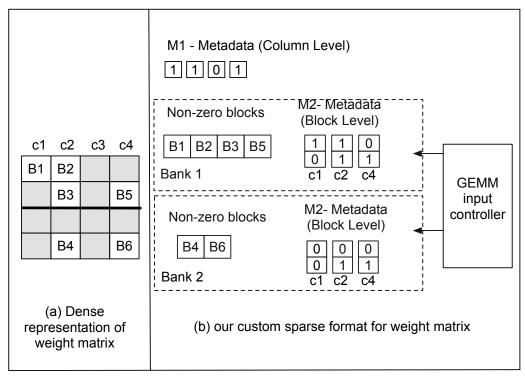

| 3.10 | An illustration of our proposed sparse format to store pruned weights and our sparsity-aware architecture                                                                                 | 76  |

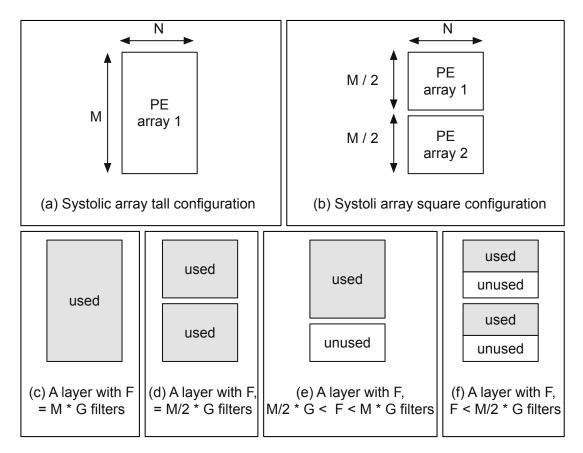

| 3.11 | An illustration of different configurations of the systolic array GEMM unit.                                                                                                              | 77  |

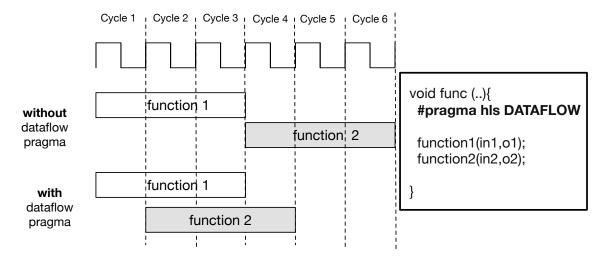

| 4.1  | An illustration of loop pipelining with HLS                                                                                                                                               | 87  |

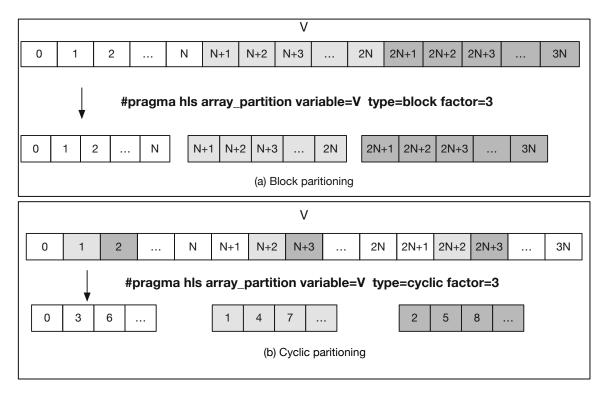

| 4.2  | An illustration of loop unrolling with HLS                                                                                                                                                | 88  |

| 4.3  | An illustration of dataflow pragma in HLS                                                                                                                                                 | 89  |

| 4.4  | An illustration of array partitioning with HLS                                                                                                                                            | 90  |

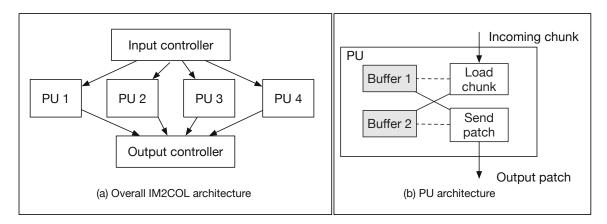

| 4.5  | A high-level overview of IM2CoL and patch units                                                                                                                                           | 92  |

| 4.6  | An illustration of the IM2CoL unit in our FPGA design for sparse CNNs                                                                                                                     | 93  |

| 4.7  | The architecture of the GEMM unit in our FPGA deisgn for sparse CNNs                                                                                                                      | 98  |

| 4.8  | An illustration of our sparse format in comparison to the CSC format 1                                                                                                                    | 101 |

| 4.9 | A demonstration of our design's flexibility in supporting CNN layers with a variety of filters                                                          |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

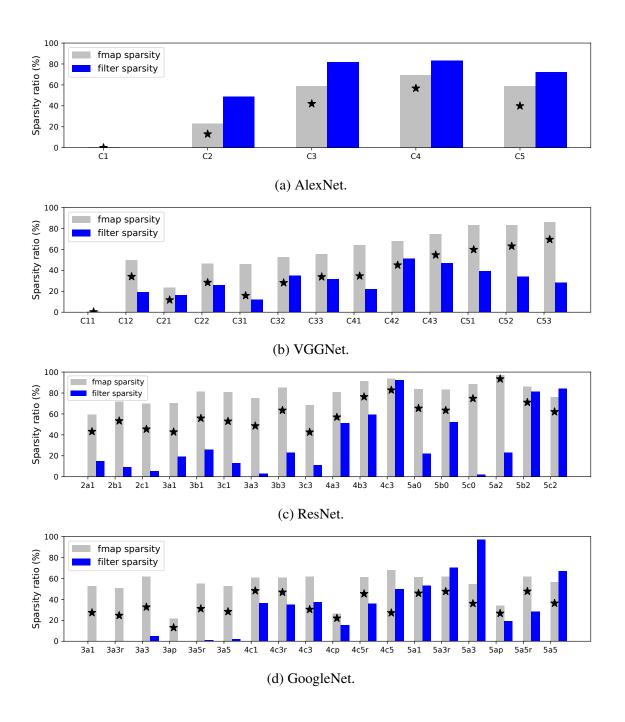

| 5.1 | An illustration showing the sparsity ratio in the filters and input feature maps for AlexNet, VGGNet, ResNet, and GoogleNet                             |

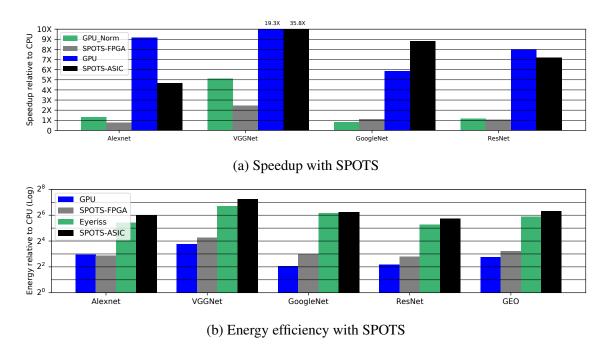

| 5.2 | Evaluating the ASIC and FPGA prototypes of SPOTS in performance and energy efficiency compared to the CPU and GPU implementations for sparse CNNs       |

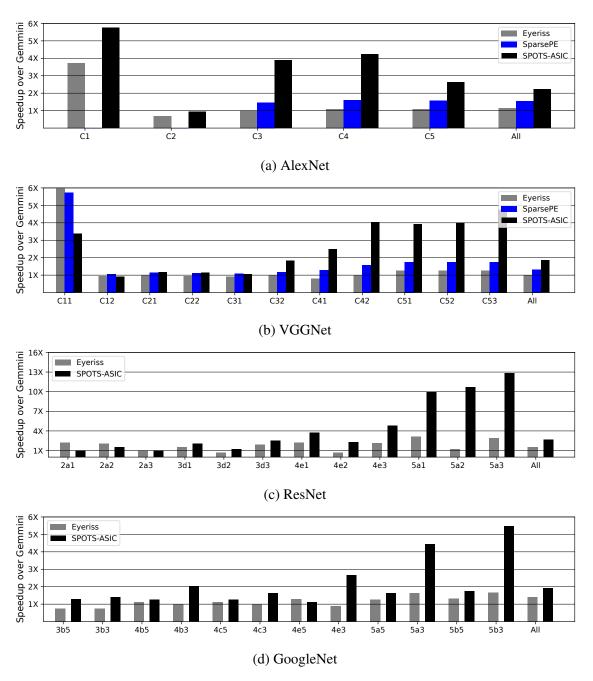

| 5.3 | Evaluating the ASIC prototype of SPOTS in performance compared to Sparse-PE, Eyeriss, and Gemmini for four CNNs: AlexNet, VGGNet, ResNet, and GoogleNet |

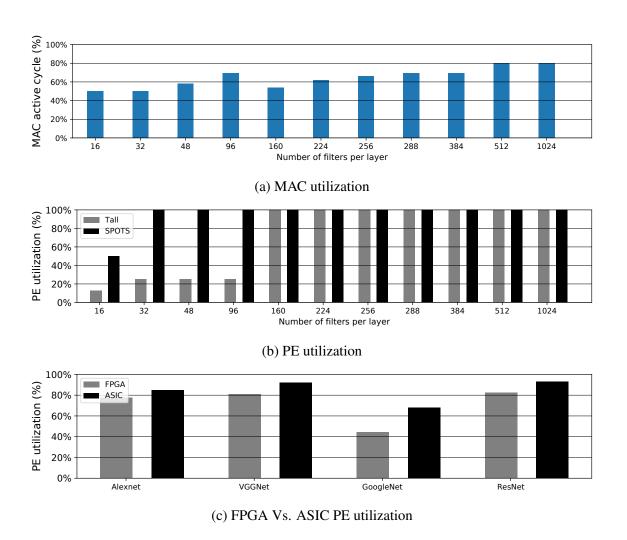

| 5.4 | Evaluating the MAC utilization for various GEMM configurations for SPOTS, ASIC and FPGA prototypes                                                      |

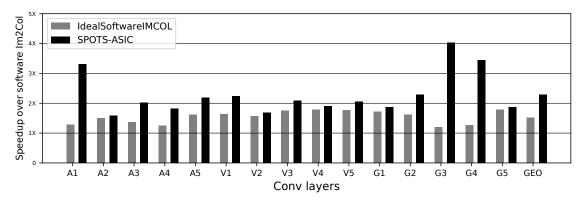

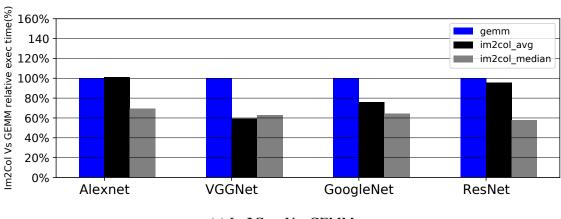

| 5.5 | Performance characterization of the IM2CoL unit in SPOTS                                                                                                |

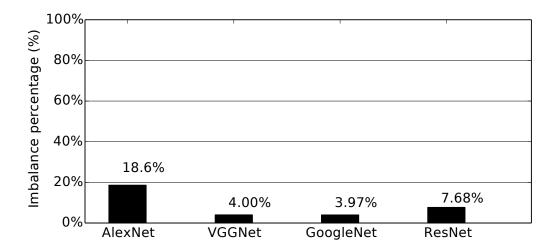

| 5.6 | The load imbalance percentage in the pruned weights for AlexNet, VG-GNet, ResNet, and GoogleNet                                                         |

#### **CHAPTER 1**

#### INTRODUCTION

Many problems from various domains, including simulating physical body dynamics [58], multigrid methods [41], network routing [153], graph processing [65], and neural networks [57] can be expressed in terms of operations on vectors and matrices. For an important class of these problems, most of the elements in the matrices or vectors are zeros. When a substantial fraction of the elements in the data is zero, the data is called sparse. A dense representation of sparse data consumes more storage and involves many unnecessary operations on zeros. Hence, it is efficient to store sparse data using a compressed format (*i.e.*, sparse format) where only the non-zero elements are stored. Sparse formats offer two advantages. First, a sparse format can reduce the total storage by orders of magnitude compared to a dense representation. In addition, operations on zeros can be skipped to reduce the overall computation.

Sparse formats store only the non-zero elements and use various techniques to encode the positions of the non-zero elements within the matrix [15, 26, 72, 91, 104, 131]. In most standard sparse formats, determining the position of the non-zero elements requires a series of indirect memory accesses that introduce irregular memory accesses. For example, to access an element A[i,j] in the Compressed Sparse Row (CSR) [104] format, one needs to consult the row pointer to obtain the location where the *row i* begins (*i.e.*,  $row\_pointer[i]$ ), search the column indices until the beginning of the next row to check if the item is present (*i.e.*, search from  $col[row\_pointer[i]]$  to  $col[row\_pointer[i+1])$ , and then subsequently access the data element at the matched index. In addition, skipping the operation involving zeros requires extra work to determine if the non-zero elements match before performing the operation. The overhead of accessing the indices into the sparse structure, not including the matching cost, can exceed the work of the mathematical operations by  $2\times-5\times[59,61]$ .

In addition to the steps involved in extracting and matching the non-zero elements in sparse data, there are other factors that make sparse computation more complex than the dense version. First, the *density* of the non-zeros in the sparse input can vary wildly for various applications. The density ratio is defined as the number of non-zero elements divided by the total number of elements in the dense representation. For example, in a neural network, the density varies across the layers anywhere from 20% to 80%. By contrast, in graph processing, the input densities are as low as  $10^{-6}\%$ . The density of non-zeros can impact the irregularity of memory accesses. Sparse data with a low-density exhibit more random access to memory. As a second factor, the distribution of non-zeros in the data referred to as the sparsity pattern affects the complexity of memory accesses in a sparse problem. It is easier to store and compute sparse data with a regular sparsity pattern (when all the non-zero values are around the diagonal). Besides, the sparsity pattern can be adjusted for some applications. For example, pruning is a method used to remove redundant weights in neural networks after training. Eliminating the weights creates zeros in the weights. Different pruning methods result in different sparsity patterns. A random pruning approach can leave zeros at any location in the input. Alternatively, a structured pruning technique leaves zeros in well-defined locations. Thus, the sparsity patterns can be controlled by choosing different pruning methods. In many other applications, the sparsity pattern cannot be altered. Furthermore, the sparse inputs in some applications can often change, with each input having a different pattern of sparsity. In contrast, the sparsity pattern of input (i.e., pruned weights) remains unchanged throughout the inference process in neural network inference tasks.

The difference in delivered Floating Point Operations per Second (FLOPs) between dense and sparse kernels can be significant depending on the density of the sparse input and the sparsity pattern [128, 142]. There have been numerous efforts to build high-performance software libraries and frameworks for sparse kernels to reduce the gap between the performance of sparse and dense versions [1, 2, 3, 76, 123, 130]. CPUs and

GPUs use a Single Instruction Multiple Data (SIMD) model to perform more useful work per instruction. Additionally, they rely on caching techniques to maximize memory performance by utilizing temporal and spatial data localities. SIMD and caching techniques are effective for most dense computations, but they are not as effective for sparse problems. Using sparse formats introduces many indirect and irregular memory accesses, which limits the benefits of caching and the SIMD model. As a result, using the same formulations and optimizations as the dense version for the sparse version results in poor performance.

For many years, Moore's Law [92] and Dennard scaling [32] helped general-purpose processors become faster and more energy efficient transparently. Dennard scaling is obsolete, and Moore's law has slowed down and is expected to end in the coming years. In response, there has been an increased interest in designing *specialized hardware*, such as ASICs and FPGAs, for various applications, including sparse problems. Specialization can be applied at different levels for sparse computation. At the algorithmic level, new algorithms and methods can be developed to perform more optimally for sparse scenarios [15, 46, 137]. For sparse data storage, the sparse formats can be customized based on the operations' memory access pattern and sparsity pattern of the inputs [38, 61, 97, 120]. Lastly, custom hardware can be designed to perform operations such as extracting the nonzero elements or matching the non-zeros more efficiently [7, 42, 52, 61]. These customizations aim to improve sparse computation's performance and energy efficiency by extracting parallelism at a finer level and optimizing the memory hierarchy to accommodate irregular memory accesses arising from sparse problems. Sparse Matrix-Vector Multiplication (SpMV), Sparse General Matrix-Matrix Multiplication (SpGEMM), and sparse neural networks are among the most studied sparse problems for these specialized hardware.

The custom hardware accelerators improve sparse problems' performance and energy efficiency at the expense of generality. Often, sparse data is subject to multiple operations, and each operation may require the data to be stored in a different format for optimal performance. For example, the COO format makes it easier to import data into a sparse

matrix since it is efficient for appending non-zeros [10]. However, SpMV performs twice as fast if the sparse input is stored in CSR instead of COO format [127]. Thus, sparse data are usually stored in standard sparse formats that are suitable for various operations. The discrepancy between the sparse format customized for an application and the format used to store the data on the memory requires a preliminary reformatting step. The data reformatting can be expensive if it cannot be amortized over multiple application executions with the same input data.

#### 1.1 Dissertation Statement

This dissertation presents a number of hardware-software techniques to improve the performance and energy efficiency of sparse linear algebra kernels, including SpMV and SpGEMM and sparse convolutional neural networks. Our general strategy is to use software methods to reformat the sparse data into a hardware-friendly format that allows the hardware to perform the computation with a high degree of parallelism. The software improves design flexibility to support multiple sparse formats, and the hardware improves performance and energy efficiency. We develop an intermediate representation that allows the software to communicate regularized data and scheduling decisions to the hardware. Besides, most of the software and hardware execution are overlapped. We applied these hardware-software techniques to three sparse problems: sparse matrix-vector multiplication, sparse general matrix-vector multiplication, and sparse convolutional neural network. Different characteristics of these three applications raise different questions, and we have answered some of them in the following contributions:

- A CPU-FPGA system to improve the performance of SpMV and SpGEMM kernels in comparison to CPU-only and FPGA-only designs, while supporting multiple sparse formats and data precisions.

- 2. An intermediate representation that enables the CPU to communicate the regularized

sparse data and the scheduling decisions to the FPGA and allow them to compute in parallel.

- 3. An ASIC and an FPGA accelerator to improve the performance and energy efficiency of sparse CNN inference task by building a hardware unit to perform IM2COL coupled with a reconfigurable systolic array-based general matrix-matrix multiplication unit.

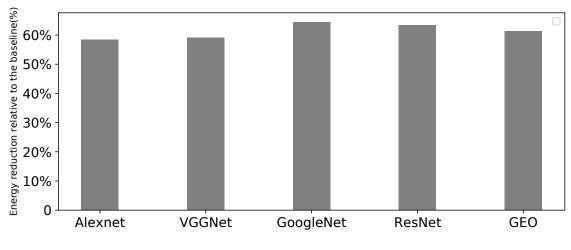

- 4. A sparsity-aware design for sparse CNNs that minimizes storage while skipping the computation involving zeros without requiring complex hardware.

#### 1.1.1 Synergistic CPU-FPGA Acceleration for SpMV and SpGEMM

Sparse linear algebra kernels such as SpMV and SpGEMM are the key components of many applications from various domains [58, 65, 153]. Many of these applications have input with very low densities (*e.g.*, below 1%). With sparse kernels, the challenge is to extract enough parallelism to improve performance while reducing storage and avoiding computation on zeros.

FPGAs offer great performance for compute-intensive applications with their programma-bility and massive parallelism. FPGAs achieve finer-grained parallelism than general-purpose architectures because they can customize memory hierarchy and computation engines for specific applications. However, most sparse problems are memory-bound due to the irregular and random nature of their memory accesses. Sparse problems suffer from low external memory bandwidth. The limited on-chip memory of FPGAs cannot fully compensate for sparse kernels' low external memory bandwidth. Hence, FPGAs cannot extract enough parallelism to compensate for their lower frequency to offer significant performance gains over general-purpose architectures for sparse problems.

These challenges can be addressed in several ways for FPGAs. One common technique is to build a sparse format customized for the FPGA's memory hierarchy and its computa-

tion engines [35, 119]. Another effective method is to use a software scheduler that analyzes the sparsity pattern and schedules non-zero input pairs to an FPGA microarchitecture to increase the resource utilization [54]. Both of these approaches can improve the performance of FPGA designs for sparse kernels by increasing their parallelism, which compensates for the lower frequency of FPGAs compared to CPUs. However, both methods require an expensive preprocessing step that involves software and cannot be overlapped with hardware computation.

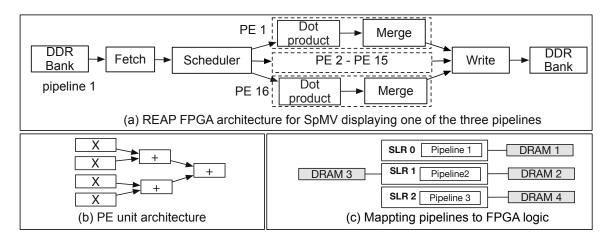

In Chapter 2, we introduce REAP, a CPU-FPGA system for sparse linear algebra that incorporates both CPU and FPGA. REAP aims to accomplish three goals. Our first goal is to support a wide range of standard sparse formats. Hardware accelerators often require data to be available in their customized format and thus do not support standard sparse formats directly [35, 38, 54, 119, 120]. Due to the disparity between the compressed format used by the accelerator and the format used to store data in memory, these approaches require a reformatting step to convert the sparse data into the hardware supported format. Data reformatting is only justified if it can be amortized over multiple program executions with the same sparse input. Further, we want the data reformatting step in software to be overlapped with the FPGA computation. Second, we want to make our design efficient and optimized for high precision inputs (e.g., Float) as well as low precision inputs (e.g., Int8), depending on the application requirement. Relaxing the data precision of sparse kernels can lead to significant performance gains [6]. Therefore, our design can be adapted to different data precisions to further improve performance. Our third objective is to propose a generic design that can be applied to a variety of sparse linear algebra kernels. There are several hardware accelerators designed for a single sparse kernel [38, 54, 97, 118, 120]. In contrast, our method is generic and can be applied to a variety of sparse kernels. The generality of our approach is demonstrated by building designs for two sparse kernels with different complexities, namely, sparse matrix-vector multiplication (SpMV) and sparse general matrix-matrix multiplication (SpGEMM).

REAP combines the strengths of both the CPU and the FPGA. To maintain high PE utilization, the CPU reorganizes sparse data into a format suitable for the FPGA. CPUs are good at manipulating small-scale, unpredictable memory access patterns as they have high clock rates and multiple levels of cache, while FPGAs with an application-specific routing and an abundant number of DSP units and on-chip memory are suitable targets to perform numerical computation on the reformatted streams of data. In the reorganization task, the CPU identifies the elements that match and schedules the computation for the FPGA. The FPGA design consists of replicated pipelines with a large number of multipliers. To convey reorganized data and scheduling information from the CPU to the FPGA, we developed a new intermediate representation. The FPGA reads the regularized data in the intermediate format. We organize the entire computation in stages to facilitate parallel execution on the CPU and FPGA. When the CPU preprocesses the data for step k, the FPGA performs the computation corresponding to step k-1. By overlapping CPU and FPGA execution, performance is further improved. An important feature of REAP is that it requires only a change to the software on the CPU to adapt to a new sparse format. Thus, we can support multiple sparse formats with a single FPGA design. In addition, our intermediate representation can be adjusted to different sparsity patterns, input sizes, and data precisions.

We have synthesized a prototype of REAP for SpMV and SpGEMM for commonly used sparse formats using the Xilinx HLS toolchain on an Alveo-U200 FPGA board. Our prototype supports CSR, ELL, and DIA sparse formats and a wide variety of precision (float, integers of various bit-widths). Our end-to-end evaluation of the system on large matrices with various sparsity patterns shows that REAP, on average, exhibits up to  $3.4 \times 1.3 \times 1.3$

Many sparse problems, such as the sparse neural network, can be reduced to SpMV

and SpGEMM computations. The design presented in Chapter 2 targets sparse problems with very low input densities (below 1%) and varying inputs. There is a need for a different hardware design to improve the performance of sparse problems with higher input densities or applications with sparse inputs that do not change frequently. A sparse convolutional neural network is one such application. Next, we describe how we apply our software-hardware approach to sparse convolutional neural networks.

# 1.1.2 An Accelerator for Sparse Convolutional Neural Networks Leveraging Systolic General Matrix-Matrix Multiplication

Neural networks are extensively used to solve complex problems in numerous domains such as video processing [68], speech recognition [23], and natural language processing [50, 113]. Convolutional neural network (CNN) is one of the most widely used neural networks. CNNs can have multiple types of layers, including convolution layers, fully connected layers, and pooling layers, with most of the computation performed in the convolution layers. Each CNN layer has multiple features, such as number of filters, kernel size, stride size, and channel size. The computation of each layer produces a higher-level abstraction of the input data, called a feature map.

To achieve higher accuracy, neural networks often include many layers. Neural networks with many layers present both performance and energy efficiency challenges to the underlying processing hardware. Luckily, most neural networks have significant redundancy that can be pruned during training without substantially reducing accuracy [48, 49]. The elimination of redundant weights will result in a network with a large number of zero values, which can potentially reduce inference computation and storage requirements. In addition to zeros in the weights, zeros also appear on the feature map while performing the inference task.

The prevalence of CNNs and the complexity of exploiting sparsity in CNNs has led to a large body of work on building hardware accelerators for sparse CNNs [8, 19, 21, 30, 36,

40, 48, 98, 102, 103, 115, 138, 145]. Given the variety of layers with different features in a CNN, it is difficult to design a hardware accelerator that performs optimally for all types of layers. Thus, some accelerators only support a few types of layer in CNNs [48, 139] or they perform optimally only for certain types of layer [21, 98]. Supporting sparse inputs makes designing CNN hardware challenging. A sparsity-aware design exploits the sparsity of one input (i.e., one-side sparsity) [8, 48, 145], or both inputs (weights and feature maps) [30, 98, 102] to enhance the performance and the energy efficiency of the sparse CNN computation. There are many ways to utilize sparsity in CNNs. First, the sparsity can be used to reduce energy consumption by gating operations involving zeros [21]. Additionally, the computation involving zeros can be skipped, improving the performance in addition to the energy consumption [30, 42, 98].

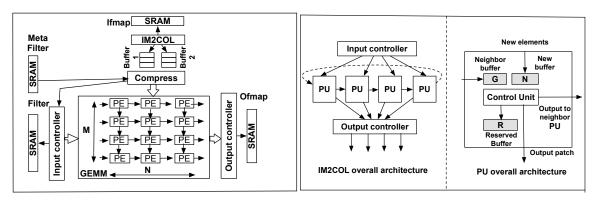

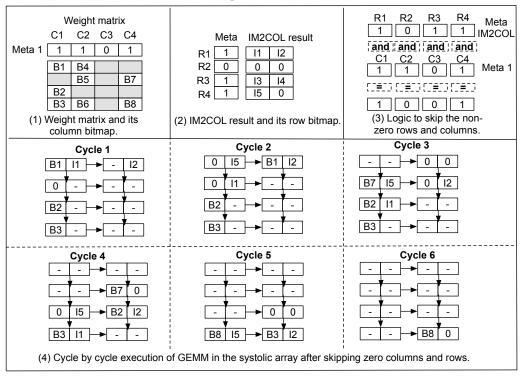

In Chapter 3 we present the details of our hardware accelerator that implements the convolution layer as a single large general matrix-matrix multiplication (GEMM) operation using an image to column transformation (IM2COL). Using GEMM as the core computation unit allows us to support a wide range of CNN layers. We discovered that the IM2COL operation accounts for a sizable fraction of the execution time (29% of the total time). Further, IM2COL performs many redundant memory accesses, contributing to the overall energy consumption. Additionally, doing the IM2COL operation in software instead of hardware prevents fine-grained pipelining of the IM2COL transformation and matrix-multiplication operations. Hence, we design both IM2COL and and GEMM units in hardware. We call our sparse convolutional network accelerator SPOTS. The three key innovations in SPOTS are: (1) a novel IM2COL unit that allows us to pipeline GEMM and IM2COL computations to improve performance, (2) a dynamically reconfigurable GEMM unit with the capability to adapt to different CNN layers and shapes, and (3) sparsity awareness that allows the design to support sparsity in both the feature map and filters. Combining these techniques increases CNN performance and energy efficiency over prior accelerators for CNNs.

A dedicated hardware IM2COL unit in SPOTS. We propose a dedicated hardware IM2COL unit that operates in parallel with the hardware GEMM unit. With the specialized IM2COL unit, we can reduce redundant accesses, resulting in faster inference speed and lower energy consumption. A novel aspect of the IM2COL unit in SPOTS is that it has a collection of patch units (PUs) that streams the input only once, performs data reorganization, creates multiple patches in parallel, and eliminates redundant accesses. Each patch unit in the IM2COL unit has three local buffers that identifies overlapped elements between patches and avoids expensive DRAM accesses. These patches are subsequently fed into a systolic array-based GEMM unit.

SPOTS is sparsity-aware. SPOTS efficiently handles zeros in both inputs: weights and the input feature map. SPOTS uses sparsity to skip data transfer and computation for zeros. By using a group-wise pruning technique with a new sparse format, we can reduce the storage requirements while still allowing high-speed access to the weights necessary to keep the PEs active. Further, SPOTS tags and skips blocks of zeros in the result of the IM2COL unit and weights before entering the systolic array, saving computation cycles and memory transfers. Finally, SPOTS can also prevent load imbalances caused by an uneven distribution of zeros in the inputs by skipping the zero blocks for all PEs.

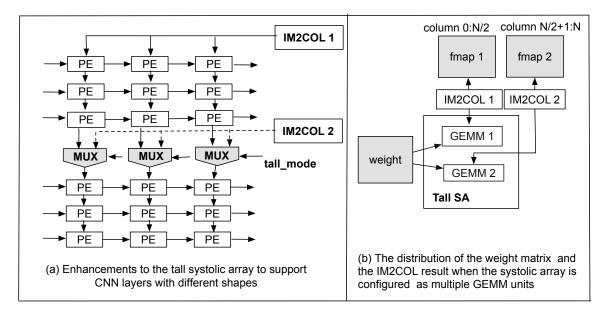

A dynamically reconfigurable GEMM unit in SPOTS. The GEMM unit in SPOTS can be configured as multiple GEMM units with square-shaped systolic arrays with processing elements (PEs) or a single tall-thin unit. The tall-thin shape better balances the memory bandwidth requirement of the GEMM unit and the IM2CoL throughput, which allows efficient pipelining of operations between the PEs performing the matrix multiplication and the PUs executing the IM2CoL reorganization. The dynamic reconfigurability of the GEMM units enables SPOTS to achieve high PE utilization for various kinds of convolutional layers that differ in number of filters, kernel size, stride size, and input dimensions. In addition to the convolution and fully connected layers, SPOTS supports pooling layers with a minor

enhancement to the IM2COL unit.

Improvement in performance and energy efficiency with SPOTS. The techniques in SPOTS improve CNN performance and energy efficiency over prior accelerators. We evaluate our design for four popular CNNs, AlexNet, VGGNet, ResNet, and GoogleNet, which features a diverse set of convolution layers with different memory and computation requirements. We compare the performance and energy efficiency of SPOTS with other state-of-the-art hardware accelerators for CNNs. Our results show that SPOTS is on average  $2.16 \times 1.74 \times 1.63 \times 1.63 \times 1.63 \times 1.63 \times 1.20 \times$

#### 1.1.3 A End-to-end FPGA Prototype of SPOTS for Sparse CNNs

Designing and manufacturing ASICs can take a long time and cost thousands of dollars. FPGAs are an alternative solution for building custom hardware. FPGA reconfigurable substrates reduce non-recurring engineering (NRE) costs and can be reprogrammed for different applications. Despite these advantages, FPGAs have some disadvantages when compared to ASICs. FPGAs operate at a lower frequency than ASICs partially due to their reconfigurability features. Therefore, FPGAs are slower than ASICs unless they can take advantage of more parallelism to compensate for their lower frequency.

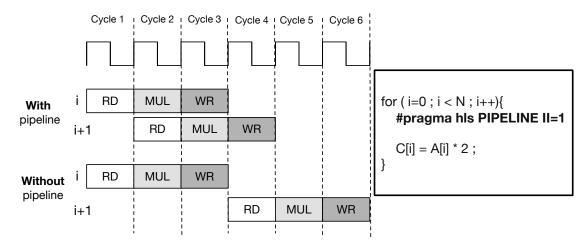

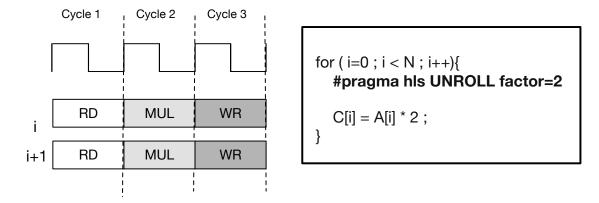

FPGAs are also constrained by the number of available resources, such as the on-chip memory. Most FPGAs have very limited on-chip memory resources compared to CPUs' multi-level caches and GPUs' on-chip memory. In Chapter 4 we present our end-to-end FPGA design for sparse convolution neural network based on our design in Chapter 3. To build our end-to-end FPGA accelerator, we borrowed some of the main design strategies from our ASIC design, such as offloading the IM2COL and GEMM computations to the

hardware and our sparsity-awareness design. However, we revisited some aspects of the design, including the design for the IM2COL and the GEMM units to better suit FPGA. There are two main advances in our FPGA design. First, our design is scalable to different FPGAs with different resource constraints. Second, unlike many prior FPGA designs, our design uses sparsity in feature maps and weight inputs without introducing additional complexity. We describe how we used the high level synthesis (HLS) tools to build an end-to-end prototype of our design. Our end-to-end evaluation on Alveo U200 FPGA shows that by exploiting sparsity in both inputs and by overlapping the IM2COL and GEMM computation, our design can achieve better or similar CPU performance with a frequency  $20 \times$  less than the CPU. Besides, our FPGA solution is more energy-efficient than the CPU and GPU implementations.

#### 1.2 Papers Related to this Dissertation

This dissertation presents the ideas and techniques presented in the following publications written in collaboration with my advisor Santosh Nagarakatte and other collaborators, Richard P. Martin from Rutgers University, Veronica Lagrange, Matt Bryson, and Xuebin Yao from Samsung Semiconductor's memory solutions lab.

- 1. "Synergistic CPU-FPGA Acceleration of Sparse Linear Algebra," [115], which presents a software/hardware technique to improve the performance of sparse matrix-vector multiplication and sparse matrix-matrix multiplication on a CPU-FPGA system.

- 2. "An Accelerator for Sparse Convolutional Neural Networks Leveraging Systolic General Matrix-Matrix Multiplication," [117] and its corresponding technical report [116] that presents our hardware accelerator for sparse convolutional neural network by proposing a novel hardware unit to perform the IM2COL transformation of the input feature map coupled with a systolic array-based general matrix-matrix multiplication (GEMM) unit.

3. "Near-Storage Processing for Solid State Drive Based Recommendation Inference with SmartSSDs." [114], which builds an inference engine for deep learning-based recommendation systems using a SmartSSD device that features an FPGA and an SSD device. Our design offloads part of the computation to the FPGA on the SmartSSD, improving performance, and energy efficiency by doing the computation near the data.

#### 1.3 Dissertation Organization

Chapter 2 provides background on sparse formats and sparse linear algebra kernels and then presents details on our synergistic hardware/software design for SpMV and SpGEMM kernels using a CPU-FPGA system. In Chapter 3, we first provide a primer on CNNs and sparsity-awareness designs. Then, we present our ASIC design for accelerating sparse CNNs inference task. Chapter 4 presents the end-to-end FPGA prototype of our accelerator for sparse CNNs. Chapter 5 evaluates the performance and energy efficiency of our ASIC and FPGA prototypes for various sparse CNNs. Chapter 6 concludes the dissertation and provide future directions.

#### **CHAPTER 2**

## SPARSE LINEAR ALGEBRA ACCELERATION FOR MULTIPLE FORMATS USING A CPU-FPGA SYSTEM

There are a variety of applications from various domains that use linear algebra kernels, including multigrid methods [41], graph processing [65], and simulating physical body dynamics [58]. In many of these applications, the majority of the elements are zeros (more than 99%). Many compressed formats (i.e., sparse formats) have been explored to avoid storing the zero elements and performing computations on them. Most standard sparse formats involve indirection and irregular memory accesses to locate and match the non-zero values, resulting in low memory bandwidth for these sparse kernels. In response to this, hardware accelerators are utilizing specialized sparse formats that cater to specific operation and input sparsity patterns. By using custom formats, these hardware accelerators are able to access the non-zero elements with higher bandwidth and extract more parallelism. Despite its benefits, this method has two main disadvantages. First, sparse data are often subject to multiple operations, and each operation may require the data to be stored in a different format for optimal performance. Thus, the inputs must be preprocessed from other formats into a hardware-friendly format before computation can begin. Second, the inputs to the application may frequently change where each input has a different sparsity pattern. Hence, customizing the sparse data storage based on the sparsity pattern of the input requires an expensive preprocessing step for each input.

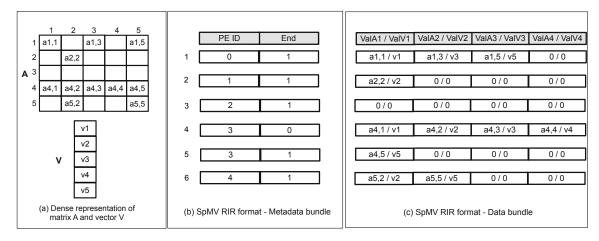

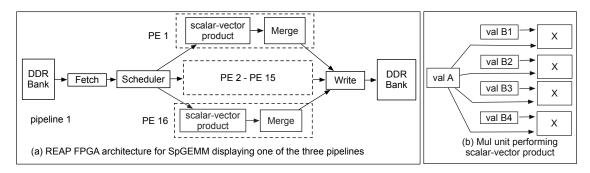

This chapter presents a software-hardware approach for high performance and adaptive computation of sparse matrix-vector multiplication (SpMV) and sparse general matrix-matrix multiplication (SpGEMM) kernels on a cooperative CPU-FPGA platform. In our design, which we call REAP, the CPU reorganizes the elements of a sparse matrix, allowing the FPGA to perform the computation with a high degree of parallelism. We pro-

pose a novel intermediate representation, which we call REAP intermediate representation (RIR), enabling the CPU to communicate the sparse data and the scheduling decisions to the FPGA. The preprocessed data in the RIR format, which is created by the CPU, removes all indirect accesses and index matching operations on the FPGA. Hence, the FPGA design can adapt to different sparsity patterns, dimensions, and data precision. To maximize performance, CPU tasks and FPGA tasks are overlapped. In contrast to prior research, our approach accelerates computation with multiple commonly used sparse formats without changing the FPGA's design, which is a significant improvement over approaches that require a custom design for each sparse format.

### 2.1 Overview of Our CPU-FPGA system for Accelerating Sparse Linear Algebra Kernels

Field Programmable Gate Arrays (FPGAs) promise to improve energy, throughput, and latency for sparse kernels, as they become more widely available in modern data centers. FPGAs are better than general-purpose architectures at exploiting fine-grained parallelism by allowing for application-specific custom memory accesses and compute engines. However, broadly realizing gains for sparse computation using FPGAs remains a challenge. Most standard sparse formats introduce indirect and irregular memory accesses, resulting in suboptimal memory throughput. The irregularity in the sparse operations also can introduce data dependencies that reduce the frequency and increase resource needs. These factors result in low compute utilization and limit the FPGA's ability to extract sufficient parallelism to achieve meaningful performance improvements over general-purpose architectures.

A large body of prior work has explored various methods to address these challenges. A common approach is to use a customized compressed format tailored to a specific FPGA's architecture. For example, recent work proposed a custom format for multi-die High Memory Bandwidth (HBM) FPGAs [35]. Another work proposed a scheduling technique that

partitions the sparse inputs into smaller batches that fit into the on-chip memory [119]. Similarly, SPAGHETTI [54] uses a pattern-aware software scheduler that analyzes the sparsity pattern and schedules the non-zero pairs of the inputs onto the fixed microarchitecture. While these studies successfully improved the performance of an FPGA for certain sparse kernels and architectures, their end-to-end performance degrades for standard sparse formats because of expensive preprocessing costs.

We propose a design with three key features to address some of the weaknesses of prior FPGA accelerators for sparse linear algebra kernels. First, our design supports a wide range of standard sparse formats. Instead of requiring a preprocessing step to convert the data from its original format to the format supported by the hardware, our design processes the input directly using the sparse format in which the data is stored. Second, our design is flexible to support both high precision inputs (*e.g.*, Float) as well as low precision inputs (*e.g.*, Int8) depending on the application's need. Relaxing the data precision of sparse kernels can result in significant performance gain [6]. Third, our approach is generic and thus can be applied to various sparse linear algebra kernels, not only a single sparse kernel.

Our design which we call it REAP is a cooperative CPU-FPGA system for sparse computation that combines the strengths of both the CPU and the FPGA. In REAP, the CPU reorganizes the sparse data into a format suitable for the FPGA to keep its computation units active. CPUs are good at manipulating small-scale, unpredictable memory access patterns as they have high clock rates and multiple levels of cache, while FPGAs with an application-specific routing and an abundant number of DSP units and on-chip memory are suitable targets to perform numerical computation on the reformatted streams of data.

The CPU identifies the matching elements that need to be multiplied and schedules the computation on the FPGA during the reorganization task. To communicate the reorganized data and scheduling information from the CPU to the FPGA, we developed a new intermediate representation called *REAP intermediate representation* (RIR). Our FPGA design consists of replicated pipelines with a large number of multipliers. The FPGA reads the

regular preprocessed data from the CPU in RIR format and performs the computation. We organize the entire computation in steps to facilitate parallel processing of the data reorganization by the CPU and the computation on the FPGA. When the CPU preprocesses the data for step k, the FPGA performs the computation corresponding to step k-1. This overlapped execution by the CPU and the FPGA further improves performance. The other important feature of our design is its ability to adapt to a new sparse format by simply modifying the software preprocessing task on the CPU. More importantly, it is not necessary to change the hardware on the FPGA to handle a new sparse format, which allows us to support widely used sparse formats with a single design. Besides, RIR can adapt to different sparsity patterns, input sizes, and data input precision.

#### 2.1.1 Contributions

The contributions to this chapter can be summarized as follows:

- We propose a synergistic CPU-FPGA system for accelerating sparse linear algebra kernels whose inputs have a high percentage of zeros.

- We propose an intermediate data representation for communication between the CPU

and FPGA that can be applied to multiple sparse kernels while supporting various

sparse formats and different data precisions.

- We propose a high performance CPU-FPGA implementation for two important sparse problems namely, SpMV and SpGEMM kernels that supports multiple sparse formats and different data precisions.

#### 2.2 Background on Sparse Formats and Sparse Linear Algebra Kernels

In this section, we first provide a brief primer on different sparse formats to store sparse matrices in a compressed form. We then provide background on sparse matrix-vector multiplication (SpMV) and sparse general matrix-matrix multiplication (SpGEMM). Finally, we review the high-level architecture of modern FPGA devices.

#### 2.2.1 A Background on Sparse Formats

In a sparse matrix, the majority of the elements are zeros. The number of non-zero elements divided by the total number of elements in a matrix is termed the *density* of the matrix. It is inefficient to store a sparse matrix in the same format as a dense matrix. Thus, researchers have explored different compression schemes (sparse formats) to avoid storing zero elements [10, 11, 15, 26, 104]. Each sparse format is ideal under certain conditions, and no single format is superior for storing sparse matrices. The ideal format depends on different factors such as the sparsity pattern, the workload, and the hardware in use. Hence, it is desirable that accelerators support multiple formats. Otherwise, extra reformatting is required to put the data into the supported format.

In this dissertation, we discuss some of the most commonly used sparse formats, such as Coordinate format (COO), Compressed Sparse Row (CSR)[104], Diagonal (DIA), ELL-PACK (ELL)[26], Bitmap Encoding [91], and Run-Length Encoding (RLC) [72]. Next, we explain each of these sparse formats.

**Coordinate** (**COO**). Coordinate format, commonly known as *COO* format [10] is the most primitive way to store the non-zero values of a sparse matrix. The COO format keeps a list of values and the coordinates (*i.e.*, row and column indices) of the non-zero elements (Figure 2.1(b)). The COO format has a minimal preprocessing cost since it only requires appending the non-zeros with their coordinates.

Compressed sparse row (CSR). The COO format redundantly stores row coordinates for every non-zero value. One way to remove these redundant row coordinates is by using an auxiliary array that keeps track of which non-zeros belong to each row. The values and columns of the non-zero elements are stored row by row in the two separate arrays. Then we store the starting offsets for all the rows in another array, commonly named *row\_pointer*

Figure 2.1: Different sparse format representations. (a) A dense representation of the example matrix (as a 2-dimensional array). (b) COO representation. (c) CSR representation. (d) CSC representation. (e) DIA representation. (f) ELL representation. (g) RLC representation. (h) Bitmap representation. Here, \* in the sparse representations indicates 0.

array. This method of storing the non-zero values is called Compressed Sparse Row (CSR) (*i.e.*, CSR in Figure 2.1(c)). The dual of the CSR format is called Compressed Sparse Column (CSC) that stores the column pointers instead of the rows, and the non-zero values are stored in column-major fashion in contrast to the row-major fashion in the CSR format (Figure 2.1(d)).

**Diagonal (DIA).** is a memory efficient format for sparse matrices where most of the non-zero elements are near the diagonal. The DIA storage format is specified by two arrays: distance and value. Here, distance is an integer array whose dimension is equal to the number of non-empty diagonals. Element i of the distance array represents the distance between the i<sup>th</sup> diagonal and the main diagonal. A positive distance suggests the element is above the main diagonal, while a negative distance indicates the element is below the main diagonal. The main diagonal has a distance equal to zero. The value is a matrix with the number of rows equal to the number of rows in the dense representation and the number of columns equal to the number of non-zero diagonals. The i<sup>th</sup>-column of the value matrix

stores the elements belonging to the  $i^{th}$  non-zero diagonal. They are stored in the rows corresponding to the dense representation. For example, the value of 1 belongs to the 1st diagonal, which has a distance of -3 from the main diagonal (see DIA in Figure 2.1(e)).

**ELLPACK** (**ELL**). is useful for matrices that contain a bounded number of non-zeros per row. ELL storage is specified by two arrays: *column* and *value*, which both have N by M dimension, where N is the number of rows of the matrix and M is the maximum number of non-zeros per row. The value and column indices of each non-zero element in row i is stored in the i<sup>th</sup> row of the value and column arrays, respectively (see ELL in Figure 2.1(f)).

Run-length Encoding (RLC). Run-length encoding (RLC) [72] compressed a given sequence of values by replacing the continuing series of the same values with a single value that shows the number of repetitions (run). For a sparse matrix, the *run* indicates the total number of zeros before (or after) a non-zero value. Thus, in RLC, a sparse matrix is identified with a list of non-zero values and their run values (Figure 2.1(g)). Each run value indicates the total number of leading zeros before the next non-zero in the list. For example in Figure 2.1(g) there are two zero values between A3 and the previous non-zero element (A2) in a row-major order, therefore the run value for A3 is 2 (the third index).

**Bitmap Encoding.** Similar to COO, the Bitmap encoding [91] stores only the non-zeros elements in the matrix. Along with the non-zero values, we need one *flag bit* for *all* the elements in the matrix including both zero and non-zero elements (Figure 2.1(h)). The flag bit indicates whether an element is zero (*i.e.*, flag=0) or a non-zero (*i.e.*, flag=1). The bitmap encoding is effective for low to moderate sparsity percentages such as sparse neural networks.

#### 2.2.2 A Background on SpMV and SpGEMM kernels

**SpMV.** In SpMV, we multiply a sparse matrix with a dense vector that produces an output vector that is also dense. Each output value is the result of a dot product between a row of the matrix and the input vector. A naive dense implementation of the SpMV ker-

Figure 2.2: Four different formulations to perform general matrix-matrix multiplication. (1) Inner product. (2) The row by row method. (3) The column by column method. (4) Outer product. The stationary input for each formulation is shown in dark color.

nel performs computations on every element of a two-dimensional matrix, including the zero elements. The naive approach introduces high computational and storage overheads. Instead, the SpMV implementation computes the dot product using the sparse representation of the matrix (*e.g.*, CSR format). The algorithm avoids unnecessary computations of zero elements by iterating only over non-zero elements. However, this approach introduces pointer-chasing operations to access the elements in the vector. The column indices of the element in the sparse matrix are used as an index to load the appropriate element of the vector (line 7 in Algorithm 1).

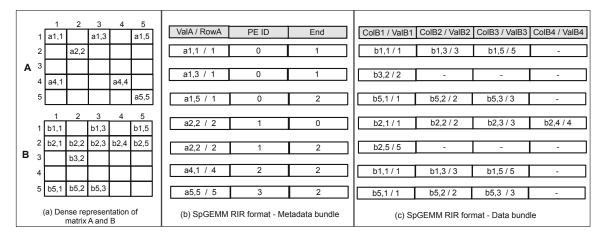

**SpGEMM.** In SpGEMM, we multiply two sparse matrices, A and B, which results in another sparse matrix (C). Based on the order (*i.e.*, row-major or column-major) in which each input matrix is accessed, there are four different formulations for a SpGEMM, as shown in Figure 2.2. We compare each formulation from four different perspectives: (1) preprocessing requirements, (2) on-chip memory requirement for the inputs and the output matrices, (3) opportunities for parallelization, and (4) data reuse. A formulation has higher data reuse if it performs more multiply-accumulate (MAC) operations per memory read/write.

Row-by-column formulation. This formulation is also known as the *inner product*. In this formulation, each element of the output is calculated by performing a dot product between a sparse row from matrix A and a sparse column of matrix B (see the inner product in Figure 2.2). The two input matrices for the inner product are accessed in two different orders (*i.e.*, one matrix in row-major order and the other in column-major order). It needs a preprocessing step if the input sparse formats are not in the expected order. The inner product has low on-chip memory demands as it needs one row of the first matrix and one column of the second matrix to compute one element of the output matrix. The dot product computation for any two distinct elements of the output matrix can be performed in parallel. For the dot product, the indices are matched for the two input sparse vectors (sparse row of matrix A and sparse column of matrix B). Since the two input matrices are highly sparse, it is possible that none of the indices match, which results in data being read without any computation. Overall, the inner product has low data reuse since the MAC operations are performed only when the indices of the non-zero elements are matched.

Column-by-row formulation. This formulation is also known as the *outer product*. In contrast to the inner product, the outer product takes each column of A and a row of B and computes partial products belonging to the entire output matrix. Given a column vector of A and a row vector of B, the outer product multiplies a given element of the column vector with all elements of the row vector to produce partial products that correspond to a row of the output and accumulates them (see the outer product in Figure 2.2). Similar to the inner product method, the two input matrices are accessed in two different opposite orders. Unlike the inner product, the first matrix is accessed in column-major order, while the second matrix is accessed in row-major order. Hence, it needs a preprocessing step if the input matrices are not in the appropriate order. As this method produces partial products for the entire output matrix that need to be accumulated in each step, the on-chip memory requirement for an outer product is high. The partial products can be computed in parallel, but accumulation needs synchronization. All read items are used with multiplication. Hence,

this formulation has the highest data reuse.

Row-by-row formulation. In this formulation, the entire B matrix is read for each row of A to produce a single row of the output matrix. Each row of A is multiplied with every row of B, one at a time, and the partial products are accumulated (see row by row in Figure 2.2). This formulation is often known as Gustavson's algorithm [46]. The core computation of a row-by-row formulation is a *scalar-vector product*. Unlike inner-product and outer product, the row-by-row formulation access both matrices in row-major order. Therefore, it can process two inputs in the same format. In contrast to the outer product, a single output row is computed at a time. Hence, the memory requirement is not as high as the outer product. However, it does require one matrix to be read multiple times. Further, all the rows of the sparse output matrix can be computed independently and in parallel.

Column-by-column formulation. In this formulation, the matrix A is read multiple times for each column of B to produce one column of the output matrix. For a given column of B, we multiply each column of A with that column of B to compute partial products and accumulate them to produce the column of the output matrix (see column by column in Figure 2.2). Both matrices are accessed in the column-major order. The memory requirements, parallelism, and data reuse is similar to the row-by-row formulation.

#### 2.3 Synergistic CPU-FPGA Acceleration

In this section, we describe the general architecture of REAP for accelerating sparse linear algebra kernels. We then describe the instantiations of REAP for two kernels: SpMV and SpGEMM. The unique aspect of our approach to accelerating sparse computation with REAP is that we divide the computation of sparse linear algebra kernels into two main tasks. The first task involves discovering the position of non-zero elements in the sparse inputs and reformatting them as regularized data in the intermediate data representation. The second task performs numerical computation on the reformatted data in the intermediate data representation. REAP uses the CPU for the first task and the FPGA for the second.

Further, the computation on the CPU and the FPGA are overlapped. When the CPU preprocesses the data for step k, the FPGA performs the computation corresponding to step k-1. Thus, the CPU and FPGA can execute in parallel, which improves performance.

For the CPU to communicate the reformatted data to the FPGA, we developed the REAP intermediate data representation (RIR). Our CPU-FPGA synergistic approach using the RIR format has three main advantages. First, reformatting the sparse data by the CPU removes all indirect accesses and index matching operations. It also allows large bursty data transfers from the CPU to the FPGA. A second benefit of the RIR format is that the same custom hardware can support multiple sparse formats. The FPGA computes using inputs in RIR format. Thus, multiple sparse formats can be supported with the same FPGA design by only changing the software. We can avoid long re-compilation times and performance regressions when adjusting the FPGA design to support a new sparse format. Additionally, it allows our approach to flexibly support different sparsity patterns, input sizes, and data input precision.

RIR has two important features - it is extensible and supports information about both data and metadata. We designed RIR to be extensible. RIR can be used to express information in multiple sparse kernels. For a given sparse kernel, the RIR format is designed with respect to the core operation of that kernel. While the core features of the RIR format remain the same for different sparse kernels, each sparse kernel has its own unique RIR structure. For the FPGA part of the design, this feature is essential to achieving optimal performance. We describe the RIR format for SpMV and SpGEMM in Sections 2.3.1 and 2.3.2.

The information exchanged between the CPU and FPGA is aggregated into a collection called the RIR bundle. In this way, we can amortize the cost of communication. RIR supports both data and metadata bundles. The data bundle includes the values and coordinates of the elements required for the kernel's core computation. The metadata provides extra information that allows the FPGA to manage the partial products and schedule the

Figure 2.3: The floorplan of XCU200 FPGA.

work among different processing elements. This requires co-designing the software and hardware such that the software on the CPU is aware of the FPGA design.